AD974x TxDAC An Introduction

-

Features

- High performance member of pin-compatible TxDAC product family.

- Excellent spurious-free dynamic range performance.

- SFDR to Nyquist.

- 83 dBc at 5 MHz output, 80 dBc at 10 MHz output, 73 dBc at 20 MHz output.

- SNR at 5 MHz output, 125 MSPS: 77 dB.

- Twos complement or straight binary data format.

- Differential current outputs: 2 mA to 20 mA.

- Power dissipation: 135 mW at 3.3 V, Power-down mode: 15 mW at 3.3 V.

- On-chip 1.2 V reference.

- CMOS-compatible digital interface.

- 28-lead SOIC, 28-lead TSSOP, and 32-lead LFCSP packages.

- Edge-triggered latches.

- Device variants available : AD9748 (8b), AD9740 (10b), AD9742 (12b), AD9744 (14b)

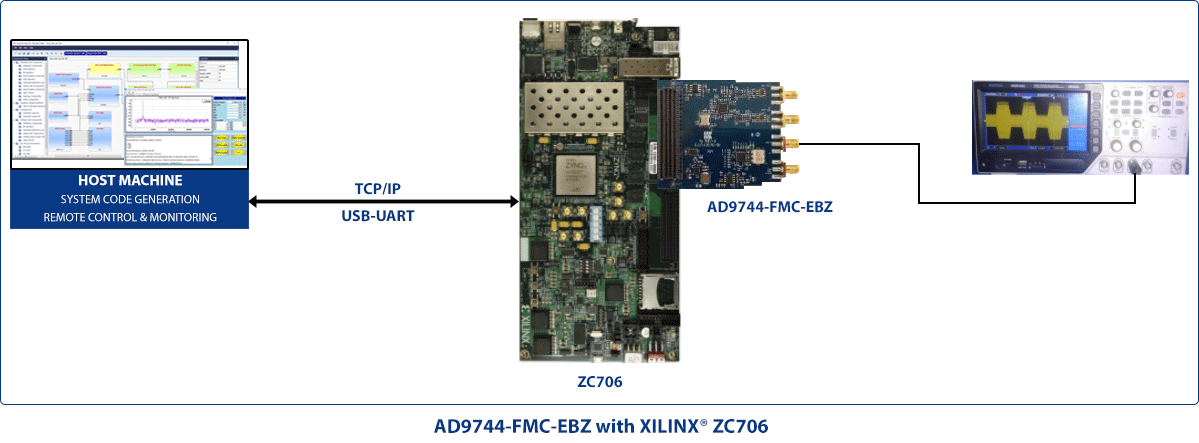

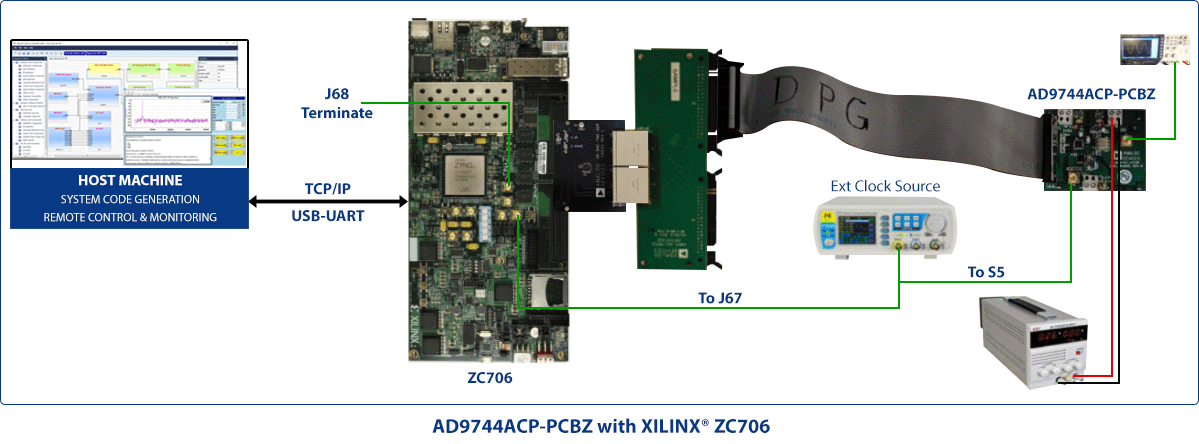

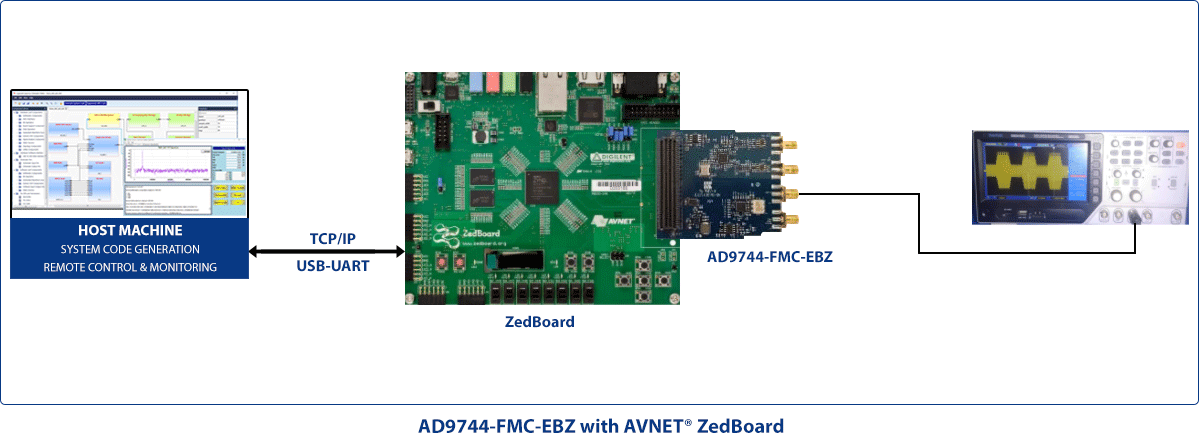

- EVAL Boards available : AD9744-FMC-EBZ (FMC HPC), AD9744-ACP-PCBZ (ADI-Custom DPG2)

- ADI Reference Page: https://www.analog.com/en/products/ad9744.html#product-overview

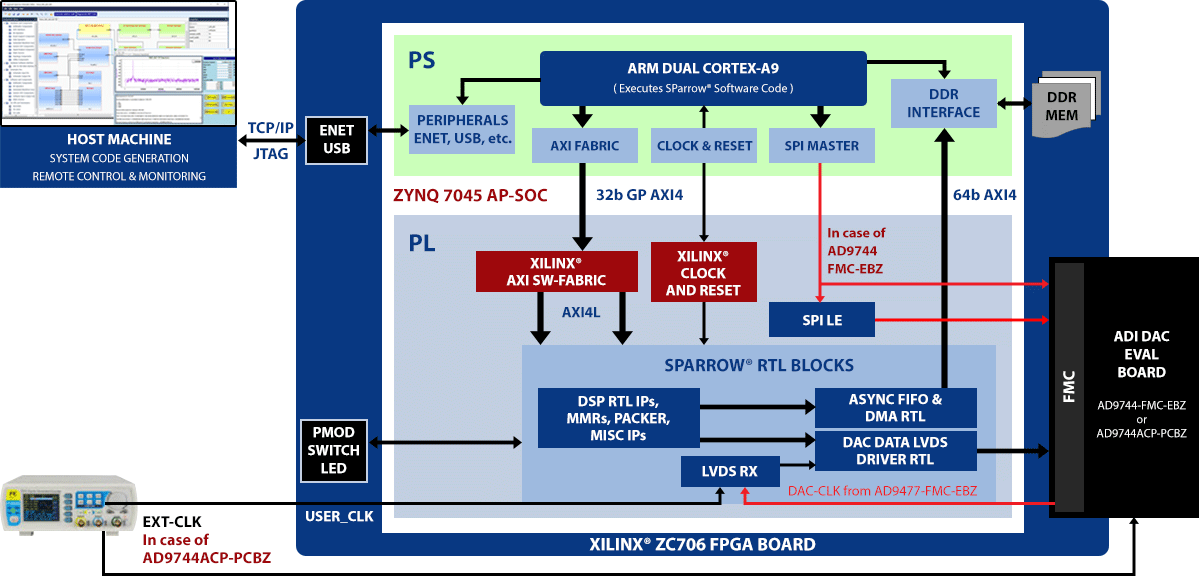

SParrow® support for AD9744

- SParrow®-AD9744 Version generates Verilog RTL IPs, C++ algorithms and C++ framework code required to interface AD9744ACP-PCBZ or AD9744-FMC-EBZ with XILINX® ZC706 or AVNET® ZedBoard.

- All TCL files and constraints required to implement the system using XILINX Vivado® tool are also auto-generated by SParrow®, so that the bit-stream can be generated directly from the RTL/C Code.

-

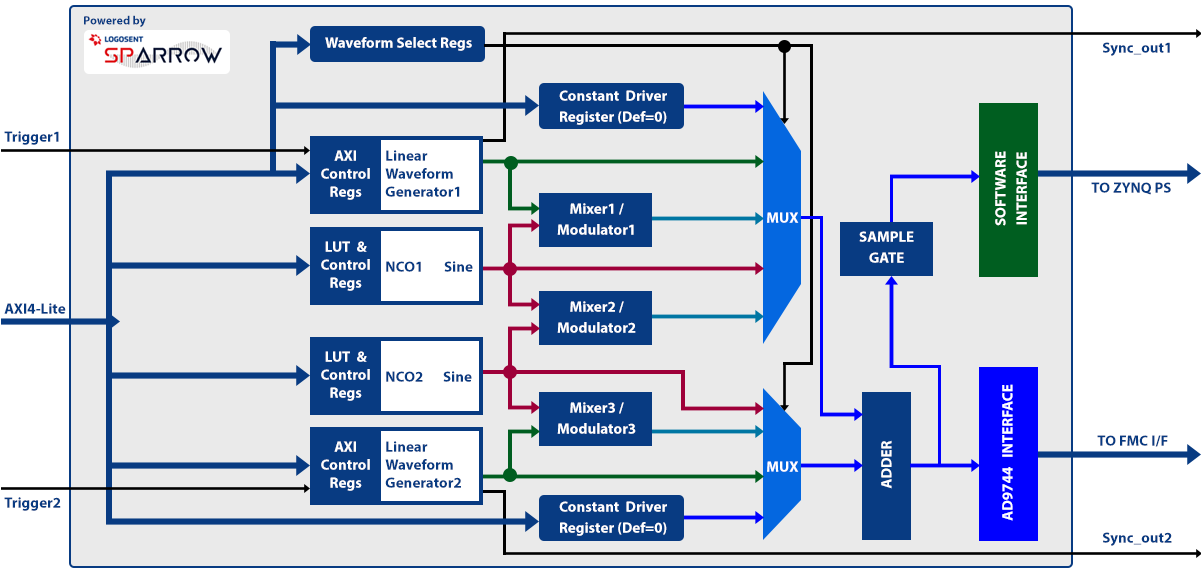

The main RTL components that are integrated into SParrow® for AD9744 support on FPGA board include:

- AD9744 Interface : An RTL Component that drives samples to AD9744 EVAL Board FMC Interface at DAC-CLK rate.

- DPG PLAYER IP : Repeatedly replays samples stored in a file (This file may be generated using DPG Software).

- RASTER NCO IP : A LUT based NCO that can be used for generating mathematically accurate Sinusoidal waveforms.

- LINEAR WAVEGEN IP : Generates various types of square, saw-tooth, triangular, trapezoidal and other linear waves.

- Basic DSP/MISC RTL IPs like ADDER, MULTIPLIER, MIXER/MODULATOR, FIR FILTER, MUX, GATES, TIMER, MMRs etc.

SParrow® – AD9744 System Architecture

Supported Eval Board + FPGA Board Pairs

Reference Design MULTI-PURPOSE WAVEFORM GENERATOR