SParrow DSP System Generation Tools

There are several tools in the industry that enable DSP system developers to generate Verilog RTL for DSP algorithms, create DSP software algorithms and also to prototype/model the DSP systems. Various reference designs are also available for targeting the DSP systems into AP-SOC/FPGA based prototyping platforms.

However, for a typical DSP system development team that lacks one or more of the required expertize/skill-sets, developing and integrating all of the above aspects to work coherently in a real time environment is no small deal. Such expertize/skill-sets include:

- Verilog (RTL) coding and verification expertize to get the full system functionality implemented in hardware.

- Knowhow on techniques to get the integrated RTL synthesize and meet timings in ASIC/FPGA.

- Expertize on software driver/firmware development and debug, for initializing the hardware.

- Expertize on DSP fixed-point algorithm C-model development and validation.

- Expertize on software driver/firmware development and debug, for initializing the hardware.

- Knowledge on how to get the DSP Systems integrated and running an AP-SOC/FPGA based prototyping boards.

- Modelling skills using tools like MATLAB®.

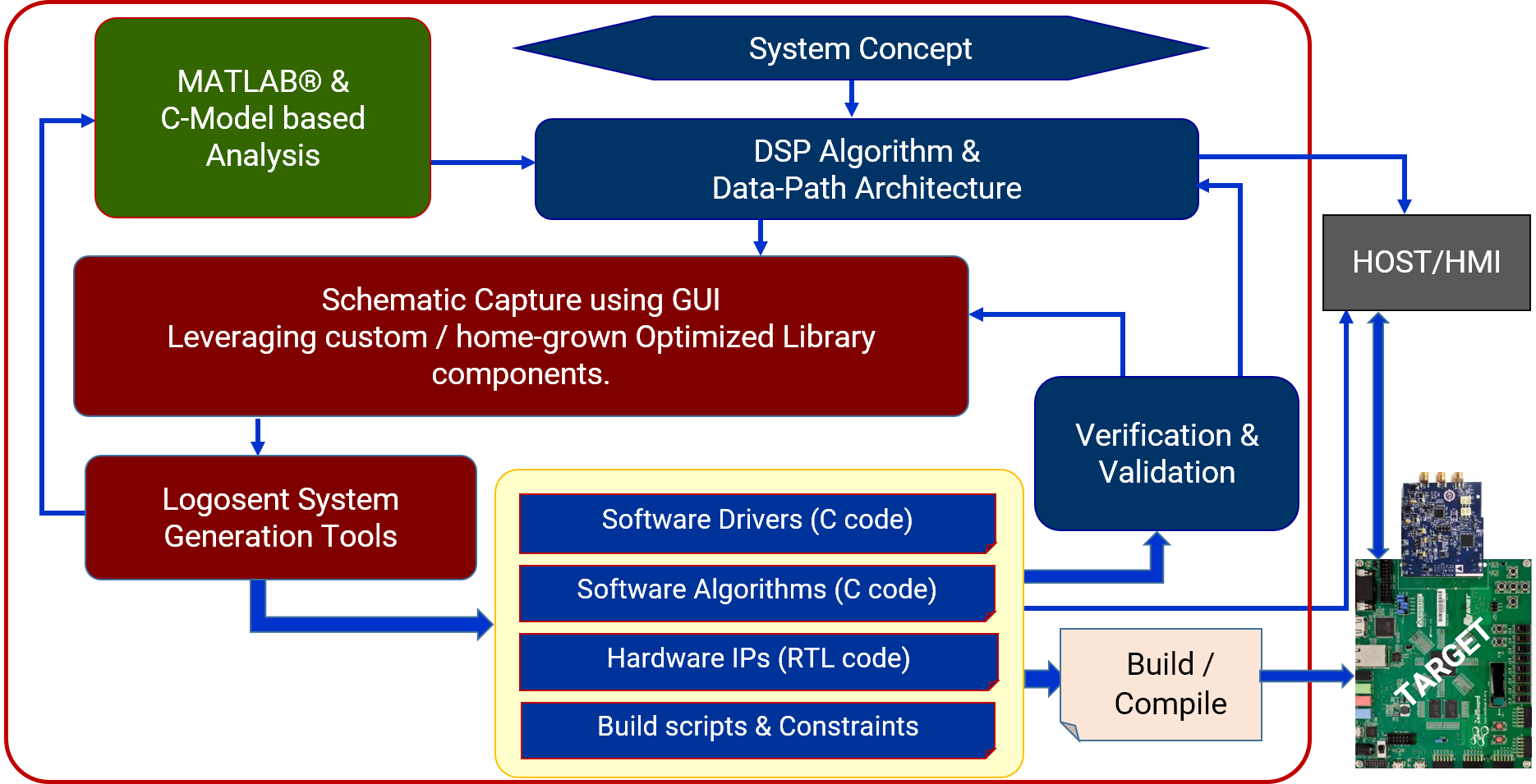

The Logosent SParrow© DSP System Generation tools are tailor-made to address the needs of such developers by integrating all of the above capabilities into a single platform. Having the SParrow at your finger tips, a lion-share (if not all) of the system generation and integration efforts can be handled with minimal time and resources. The SParrow can generate fully synthesizable Verilog RTL (both the leaf-components and the top-level wrapper), corresponding C++ Drivers and optimized fixed-point C++ Algorithms from a user-defined schematic, entered using an easy-to-use GUI. Limited MATLAB® DSP model generation capabilities are also supported in some versions.

Automated system integration with select AP-SOC/FPGA and ADC/DAC boards is made available in certain versions of SParrow. This capability allows the SParrow users to quickly implement/validate the designs on prototyping platforms, without having to spend significant time and efforts for system deployment on such boards. Along with the DSP System RTL and C code, SParrow generates the ADC/DAC interfaces, connectivity TCL files, constrains, build-scripts etc. that are required to map the system on to the supported boards.

Logosent SParrow – Some Salient features

Hardware (RTL) generation and integration

- Automated connectivity of side-band signals like Clocks, Resets, Pipe-Flush, Interrupts etc.

- Customizable cascaded AXI4Lite switch-fabric for minimizing external AXI4Lite interfaces.

- Fully Asynchronous AXI-Clock and DSP-System-Cock operation, with 2-stage synchronization.

- Automated merger of hand-instantiated Memory Mapped Registers into single AXI4Lite i/f.

- Logosent proprietary lighter stream protocol (compared to AXIS) for area/timing optimization.

- Fully behavioral RTL Reusable across platforms and optimized for achieving best timing closure.

- Supports generation of schematic-specific RTL Test-Bench templates for RTL simulations.

Software (C++) generation and integration

- Automated connectivity from hardware DMA target buffers to software algorithm inputs.

- Automated mapping of Interrupts to the corresponding Interrupt Service Routine templates.

- Generated C++ components include basic DSP functions and waveform generators.

- Specially designed algorithm and driver APIs for easy integration into user applications.

- Programmable processing buffer size to match DMA block sizes.

- The generated hardware drivers support both boot-time and run-time programmability.

- The generated C++ algorithms can be easily ported across processors and systems.

System Schematic Entry

- Supports both hardware (Verilog RTL) and software (C++) components in a single schematic.

- Supports configuring each component to the user-specified parameters from its property-pane.

- Innovative Drag-n-Drop MMR registers with user-specified offsets for hardware control/status.

- Entire bus-protocols abstracted into single-line data-path connectivity between components.

- Automated connection compatibility and schematic completeness checks to minimize iterations.

- Customizable and scalable component library, supports integration of user-specific libraries.

- Supports multi-layer hierarchy for ease of schematic development and modular design (PLUME).

Our Differentiation – Hardware IPs

- A rich set of leaf-library components and composite IPs optimized to address the needs of various DSP domains like RF, Test & Measurement, Audio and Sensors.

- Highly performance-optimized RTL to achieve the best clock-rates in mapping to ASIC or FPGA. (Proven up to 250MHz/250MSPS operation in XILINX® Zynq7000 series 28nm FPGAs)

- Uniquely pipelined architecture for supporting input sample-rate equal to the functional clock-frequency, even for complex arithmetic operations like square-root and division.

- Specially coded RTL to facilitate direct mapping of arithmetic functions to pre-defined MAC structures like DSP-Slices in FPGAs and ASIC libraries.

- Proprietary streaming bus architecture for seamless connectivity (zero glue-logic, zero clock-cycle loss) between individual components, with full data-throttling and AXI4 external i/f support.

- All Hardware IPs and Sub-Systems qualified through a three-stage V&V process:

- Extensive RTL simulations.

- Bit-accuracy comparisons against MATLAB/C models.

- At-speed validation on FPGA platforms integrating High-Speed signal sources.

Optimized Fixed-Point C Algorithms for achieving lowest compute-resource utilization

- Generic DSP Algorithms including:

- Sources – Sine, Chirp, White/Colour Noise, AM, FM, etc.

- Filters – Generic FIR, IIR, etc.

- Multi-rate FIR, Half-band IIR, CIC, etc.

- DDC, DUC, DSS, etc.

- FFT and related transformations, like Zoom-FFT, CZT, etc.

- Dynamic processing, Windowing and filtering.

Logosent SParrow based Rapid Prototyping System