SParrow® for ADI Converters An Introduction

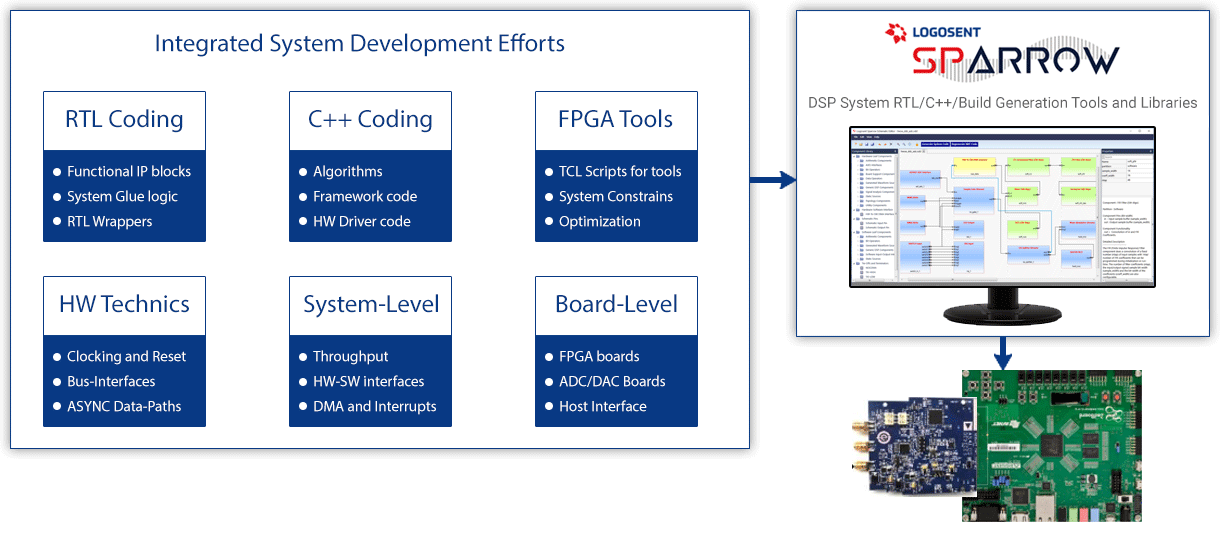

- SParrow® enables generation and deployment of FPGA reference designs for ADI Converters. Reference designs help bypass several months of efforts in implementing basic FPGA interfaces and software framework for Prototype bring-up.

- Reference designs include EVAL Board Interface RTL IPs, basic DSP RTL IPs, C++ Framework, C++ Drivers and complete build environment required for bring-up of Converter EVAL Boards paired with industry-standard FPGA platforms.

- SParrow® Tool makes the reference designs easily configurable and customizable to various prototyping requirements.

- SParrow® provides an off-the-shelf library of highly speed-optimized RTL algorithms and software drivers for developing base systems.

- The RTL and C++ code generated by SParrow® are very readable and editable so that the base system code can be easily ported to custom FPGA boards or modified to integrate user-specific IPs for building larger systems.

- SParrow® reference designs come with a prebuilt software framework for interfacing the FPGA board with a Host/PC through either Ethernet or Serial Interface.

SParrow® supported ADI Converters and FPGA Boards

| Converter | EVAL Boards | FPGA Prototyping Platforms |

|---|---|---|

| AD974x (8b, 10b, 12b, 14b, 210MSPS TxDAC) | AD9744-FMC-EBZ, AD9744ACP-PCBZ | XILINX® ZC706, AVNET® ZedBoard |

| AD9467 (16b, 250MSPS ADC) | AD9467-FMC-250EBZ | XILINX® ZC706, AVNET® ZedBoard |

The SParrow® Value Addition

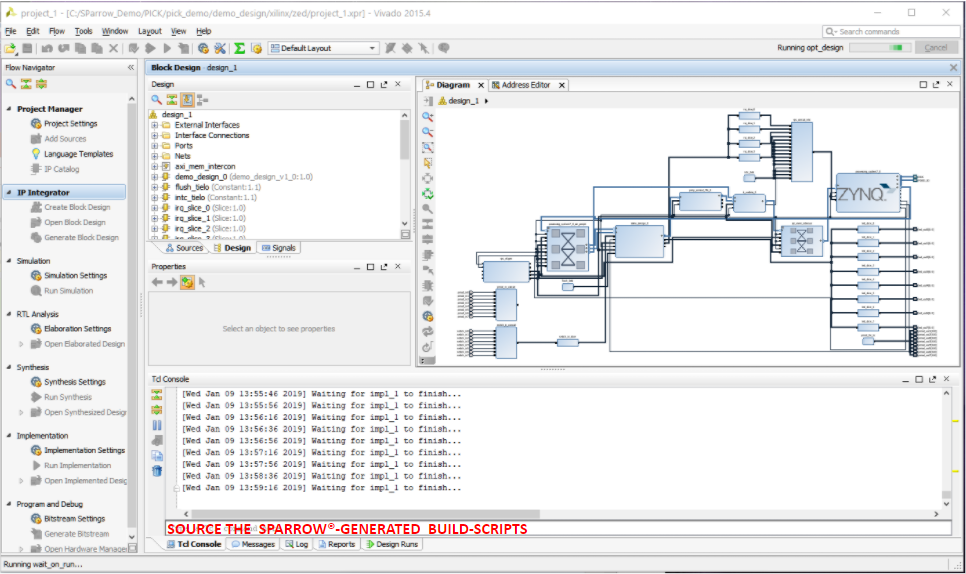

How does SParrow® Work

The

5-Step Flow

5-Step Flow

STEP 1

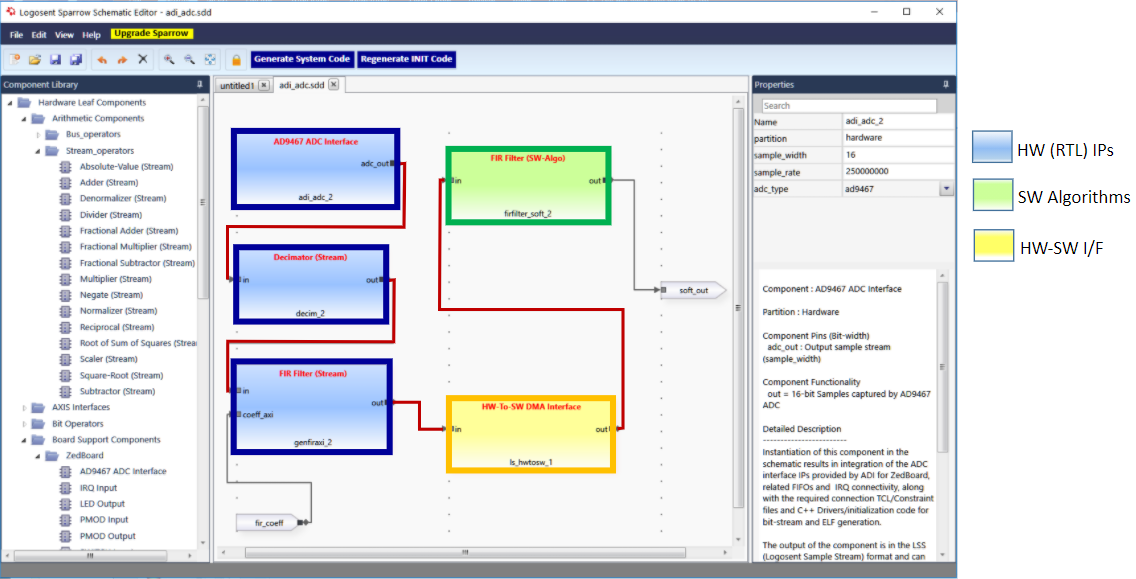

Capture the System Schematic using GUI

STEP 2

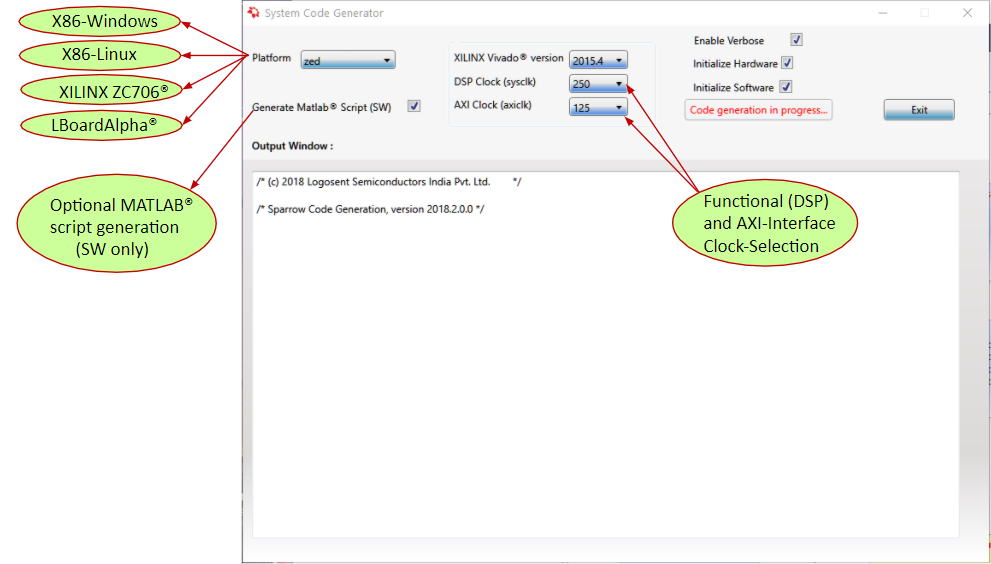

Generate System Code and build Scripts

STEP 3

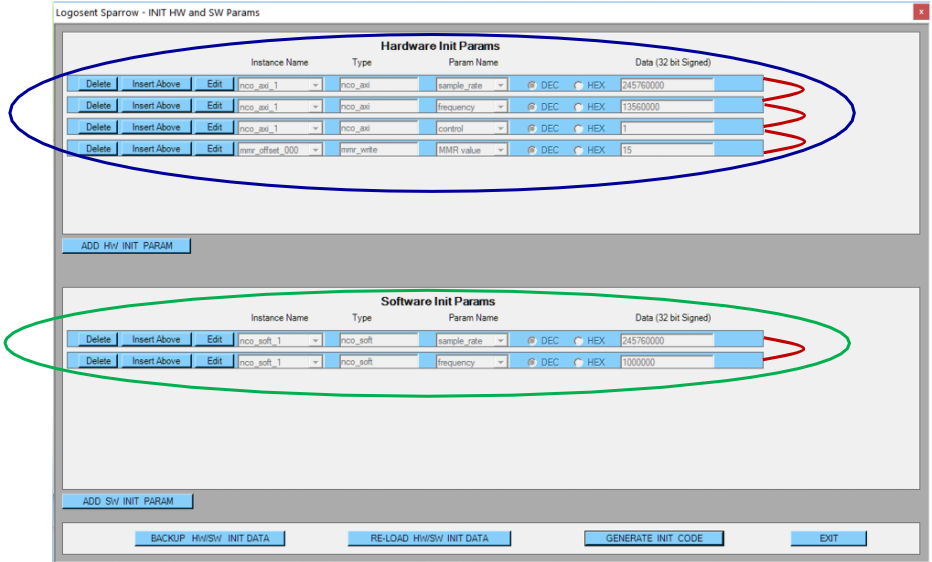

Enter System Initialization Parameters

STEP 4

Generate Bit-Stream and Executables

STEP 5

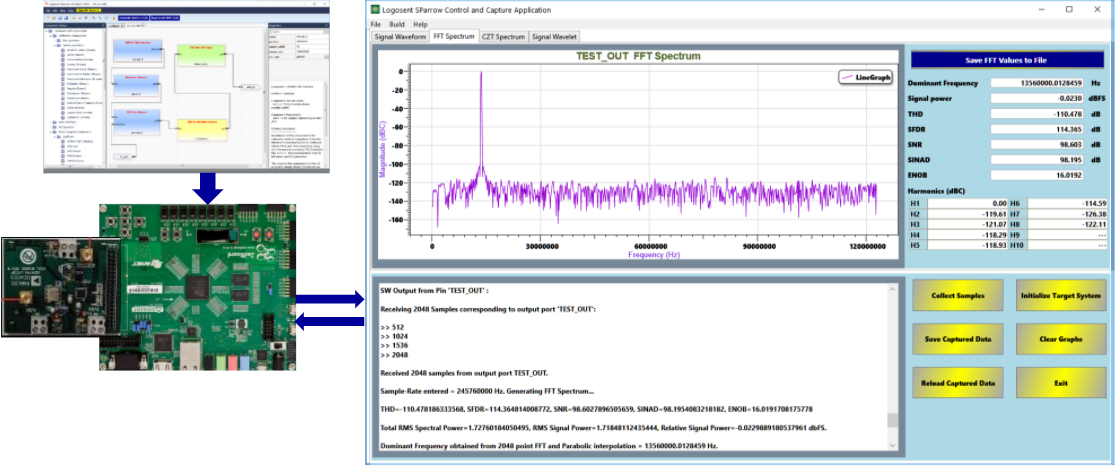

Launch the system and Capture Samples

Capture and Analyze samples from PC

The SParrow® DSP Library – A Snap-Shot

| Category | Currently supported Algorith Components (Not all components listed) |

|---|---|

| Basic Arithmetic | ADDER, SUBSTRACTOR, MULTIPLIER, ABSOLUTE-VALUE, NEGATION, NORMALIZER, DE-NORMALIZER |

| Advanced Arithmetic | FRACTIONAL ARITHMETIC, SQUARE-ROOT, ROOT-OF-SUM-OF-SQUARES, DIVISION, RECIPROCAL |

| Bit Operators | AND, OR, XOR, INVERT, SHIFTER, BIT-SPLITTER, BIT-MERGE |

| Sample Stream Operators | BUS-SLICE, BUS-MERGE, BUS-MULTIPLEX, SAMPLE-PACKER |

| Basic DSP Components | SINGLE/MULTI-SLICE FIR FILTERS, CASCADED-INTEGRATOR-COMB (CIC) FILTER, MOVING AVERAGE, DECIMATOR, MIXER,MODULATOR, DELAY |

| Composite DSP Algorithms | DYNAMIC DOWN CONVERTOR (DDC), ENVELOPE EXTRACTION/ANALYSIS, FUNCTION GENERATOR |

| Signal Analysis | DESCRETE FOURIER TRANSFORM, PERIOD/DUTY-CYCLE DETECTOR |

| Signal Sources | NCOs, LINEAR WAVE_GENERATOR |

| Utility Components | MEMORY MAPPED REGISTERS (MMR), TIMER+PWM, ASYNC-FIFO, SAMPLE-GATE, AXI4-LITE SWITCH |

- The RTL DSP components are fully-pipelined to handle maximum sample rates and proven up to 250MSPS @ 250MHz clock-rate in 28nm Zynq FPGA.

- The bit-accuracy of all HW Algorithm IPs are verified against MATLAB Models, in addition to standalone RTL testbench based simulations.

www.apteka-ed.com.ua/viagra-generic-medikament-dlya-potencii/www.apteka-ed.com.ua/viagra-generic-medikament-dlya-potencii/

https://clubgti.com/wp-content/pages/?how-to-deal-with-disputes-at-non-gamstop-casinos.html